There are two basic types of digital design methodologies:

- top-down design methodology

- bottom-up design methodology.

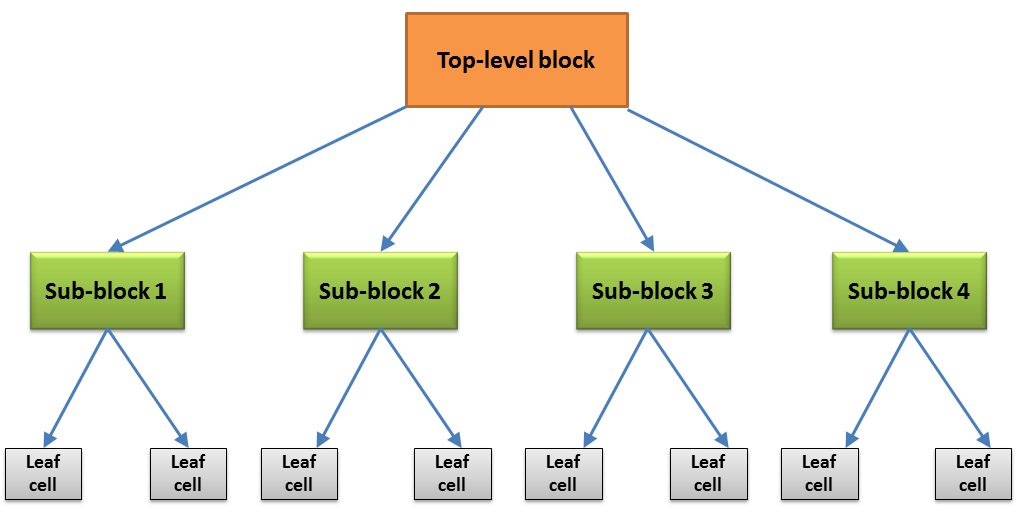

top-down Design Methodology

In a top-down design methodology, we define the top-level block and identify the sub-blocks necessary to build the top-level block. We further subdivide the sub-blocks until we come to leaf cells, which are the cells that cannot further be divided.

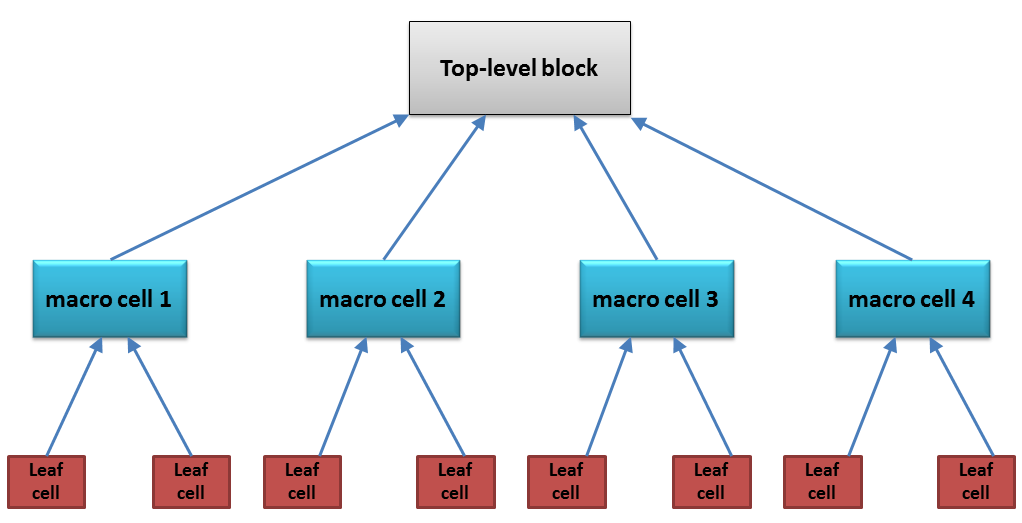

bottom-up Design Methodology

In a bottom-up design methodology, we first identify the building blocks that are available to us. We build bigger cells, using these building blocks. These cells are then used for higher-level blocks until we build the top-level block in the design.

Read Four Different Coding Styles of Verilog Language

Typically, a combination of top-down and bottom-up flows is used. Design architects define the specifications of the top-level block. Logic designers decide how the design should be structured by breaking up the functionality into blocks and sub-blocks. At the same time, Circuit designers are designing optimized circuits for leaf-level cells. They build higher-level cells by using these leaf cells. The flow meets at an intermediate point where the switch-level circuit designers have created a library of leaf cells by using switches, and the logic level designers have designed from top-down until all modules are defined in terms of leaf cells.

For example; A low leakage 4-bit parallel adder is to be designed. The logic designers would break the 4-bit parallel adder to four 1-bit full adders. Each full adder would be broken into two half adders and an OR gate. Each half adder would again be divided into one XOR gate and one AND gate. At the same time the Circuit designer would design the optimized low leakage logic gates: AND, OR and XOR from the transistor / Switch level.

Reference: Verilog HDL, A guide to Digital Design and Synthesis; Samir Palnitkar