Problem Statement:

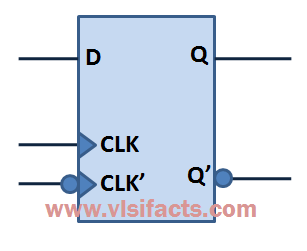

Design a circuit for an edge triggered 4-bit binary up counter (0000 to 1111). When it reaches “1111”, it should revert back to “0000” after the next edge. Use positive edge triggered D flip-flop (shown in the below figure) to design the circuit.

| Pin | Input / Output | Description |

| D | Input | Data Input |

| CLK | Input | Clock Input |

| Q<3:0> | Output (4-bits) | Count Output |

Solution:

The flip flop to be used here to design the binary counter is D-FF.

Let’s draw the excitation table for the D-FF

| Present State (Q) | Input (D) | Next State (Q+) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

The characteristic equation for the D-FF is: Q+ = D

We need to design a 4 bit up counter. So, we need 4 D-FFs to achieve the same.

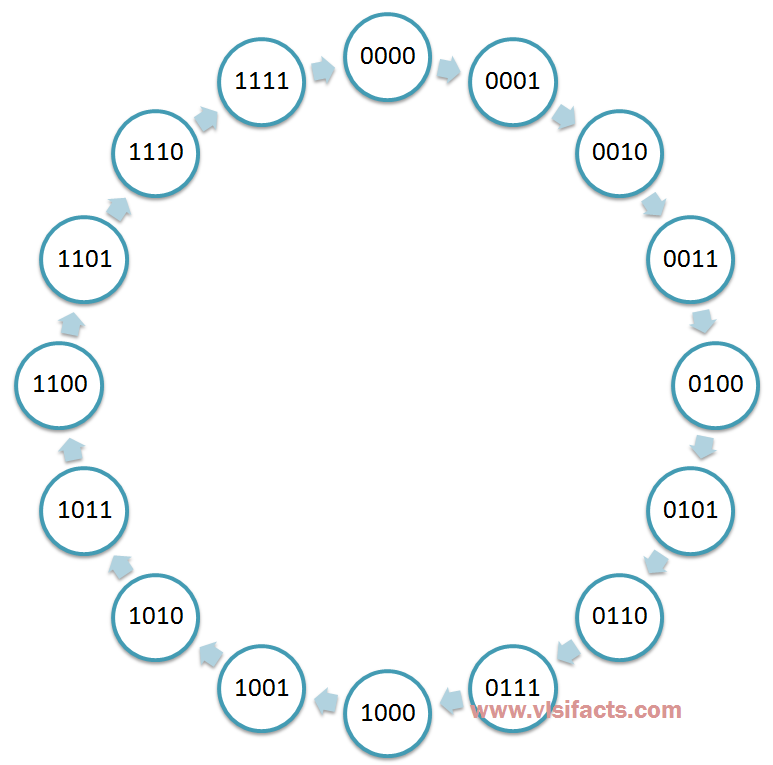

Let’s draw the state diagram of the 4-bit up counter

Let’s construct the truth table for the 4-bit up counter using D-FF

| Present State

(Q3 Q2 Q1 Q0) |

Next State

(Q3+ Q2+ Q1+ Q0+) |

D3 | D2 | D1 | D0 |

| 0000 | 0001 | 0 | 0 | 0 | 1 |

| 0001 | 0010 | 0 | 0 | 1 | 0 |

| 0010 | 0011 | 0 | 0 | 1 | 1 |

| 0011 | 0100 | 0 | 1 | 0 | 0 |

| 0100 | 0101 | 0 | 1 | 0 | 1 |

| 0101 | 0110 | 0 | 1 | 1 | 0 |

| 0110 | 0111 | 0 | 1 | 1 | 1 |

| 0111 | 1000 | 1 | 0 | 0 | 0 |

| 1000 | 1001 | 1 | 0 | 0 | 1 |

| 1001 | 1010 | 1 | 0 | 1 | 0 |

| 1010 | 1011 | 1 | 0 | 1 | 1 |

| 1011 | 1100 | 1 | 1 | 0 | 0 |

| 1100 | 1101 | 1 | 1 | 0 | 1 |

| 1101 | 1110 | 1 | 1 | 1 | 0 |

| 1110 | 1111 | 1 | 1 | 1 | 1 |

| 1111 | 0000 | 0 | 0 | 0 | 0 |

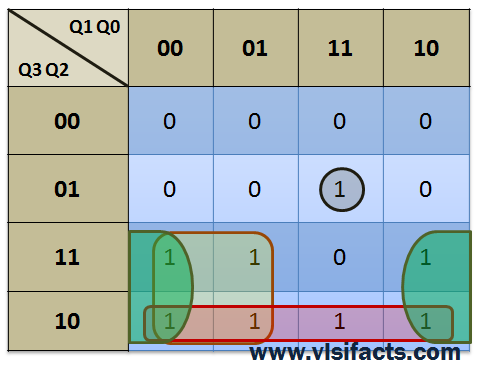

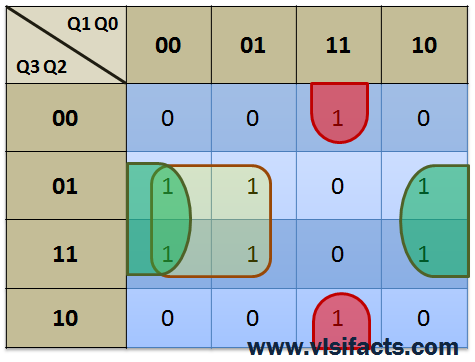

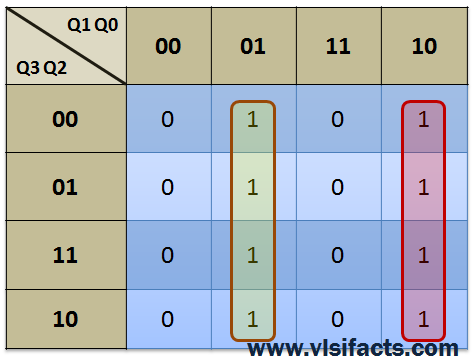

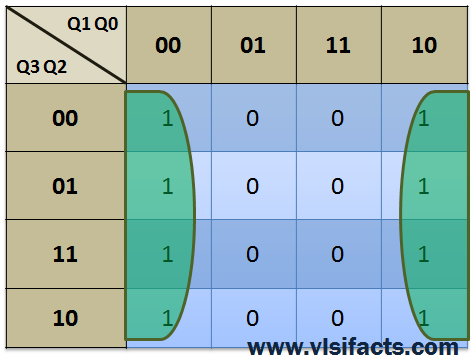

Now constructing the K-Maps and finding out the logic expressions for D3, D2, D1, D0

| D3 | D2 |

|

|

| D3 = Q3Q2′ + Q3Q0′ + Q3Q1′ + Q3’Q2Q1Q0 | D2 = Q2Q0′ + Q2Q1′ + Q2’Q1Q0 |

| D1 | D0 |

|

|

| D1 = Q1’Q0 + Q1Q0′ = Q1 ⊕ Q0 | D0 = Q0′ |

So, we found the value of D3, D2, D1, D0 in terms of Q3, Q2, Q1, Q0.

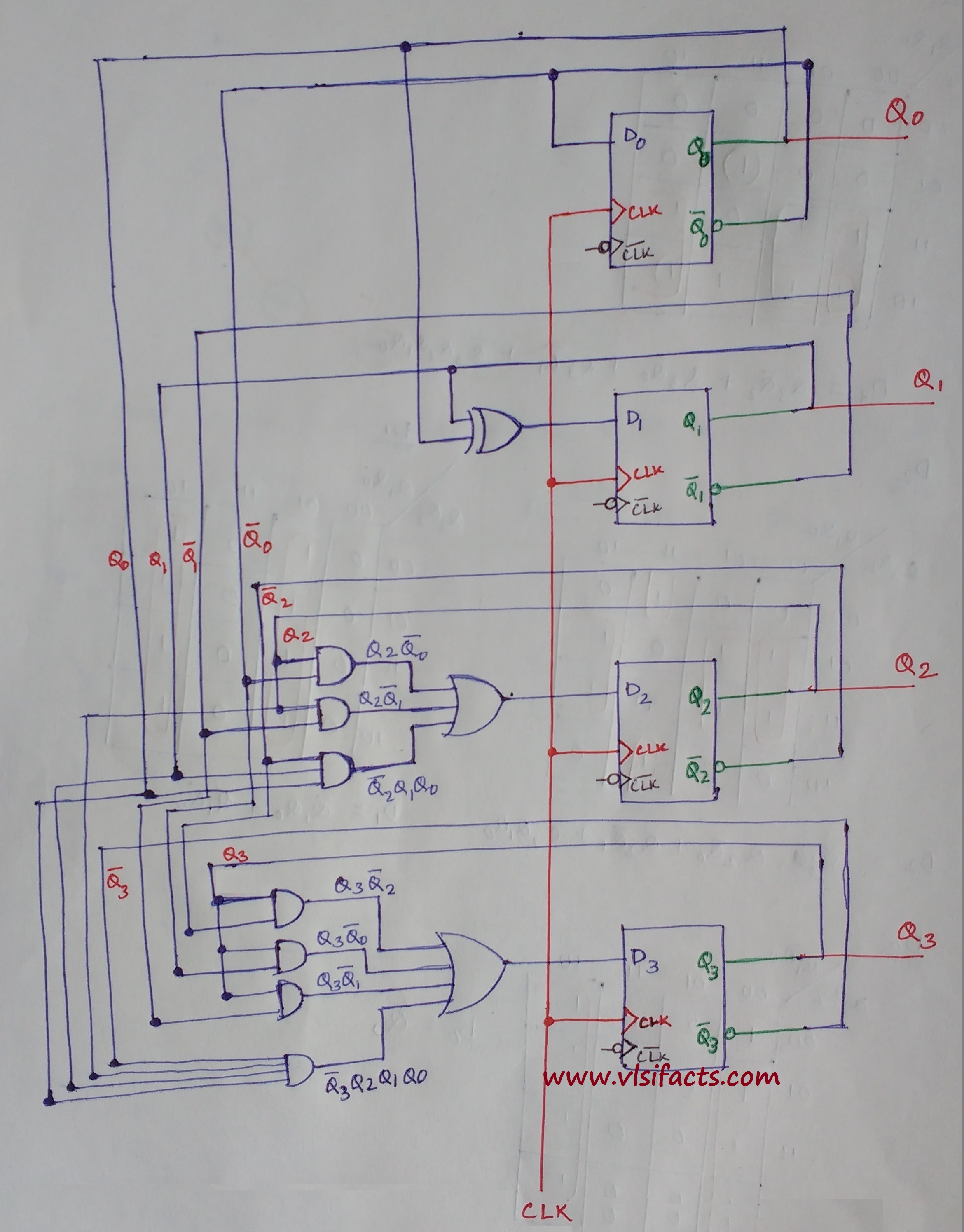

Let’s draw the designed circuit of the 4-bit up counter using D-FF

The counter output would be collected from Q3, Q2, Q1 and Q0.

The counter output would be collected from Q3, Q2, Q1 and Q0.

22 comments for “Circuit Design of a 4-bit Binary Counter Using D Flip-flops”