This process checks the connection of the n-well and p-substrate.

The C5 process used here is an n-well process. The p-type substrate is common to all NMOS devices and should be grounded.

One of the electrical rule checks (ERCs) is to verify that the p-well (in this case p-substrate) is always connected to ground.

Further, in this n-well process, if the design contains only digital circuits then the n-well should be connected to VDD.

For Well Check execute Tools –> ERC –> Check Wells or press W (as we have bounded this key to Well Check).

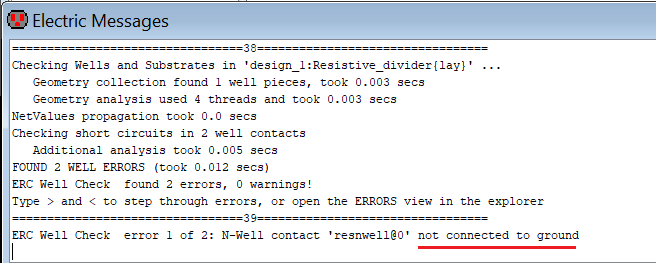

When Well Checked for the design Resistive_divider, following error has occurred.

The reason is as below:

In Digital Design all the N-Wells to be connected to VDD and all the P-Wells to be connected to Ground.

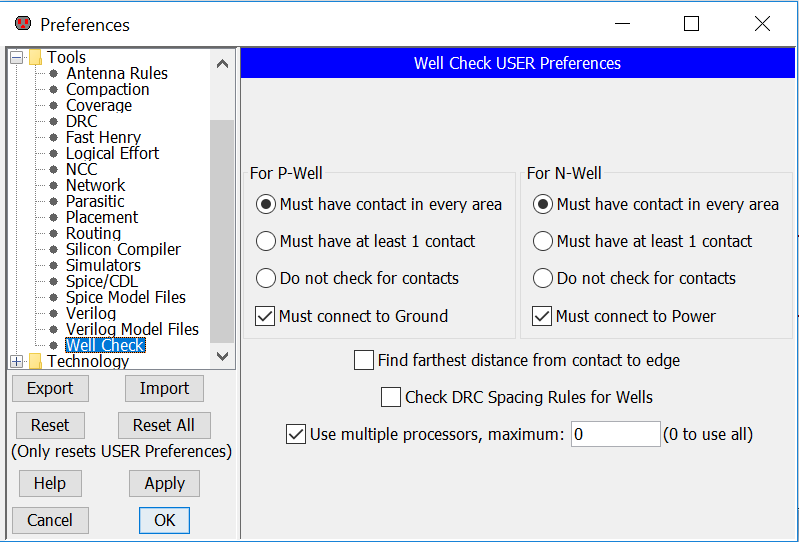

If we will go to the setup of ERC Well Check as Preferences -> Tools -> Well Check as seen below:

Here we can see For N-Well, Must connect to Power is checked.

But this Resistive_divider is not a digital design. Here the N-Well is used as a resister which is an anlog design.

So uncheck “Must connect to Power” under “For N-Well”. You will find zero Well Check error.