Here are some examples on blocking and non-blocking assignments in Verilog, that can be really useful for the budding design Engineers. First let us discuss the features of these assignments.

- They are procedural assignments always used in a procedural block like initial or always.

- In BA (Blocking assignment) RHS of the assignment is assigned immediately to the LHS in the active region of the scheduler, that is to understand we can say the assignment is immediate and it does not wait for the procedural block to end. While in NBA (Non-Blocking Assignments) the RHS is calculated first, then it is assigned to the LHS much later in the scheduler, that is to understand after the completion of procedural block (initial or always). Other wise we can say that they get executed in the NBA part of the scheduler which is second last in the sequence after Active and Inactive. .

- In BA, assignments are done in the sequence in which they are written, In NBA all the RHS are calculated and stored in the temporary memory of the compiler and then are assigned to the LHS, at the same time, that is there is no set order of assigning, it depends on the compiler.

The following example illustrates the Blocking Assignment

initial begin a=1; b=0; y=1; // at 0 simulation time y gets value '1'. #5 y=a&b; // at 5 time units y gets updated to a&b, i.e. 1&0=0 z=y; // at 5 time units z gets updated to y value, i.e. '0' #5 temp=a; // temp gets the value of a, i.e. '1' at 10 time units end

Wave forms for the above example

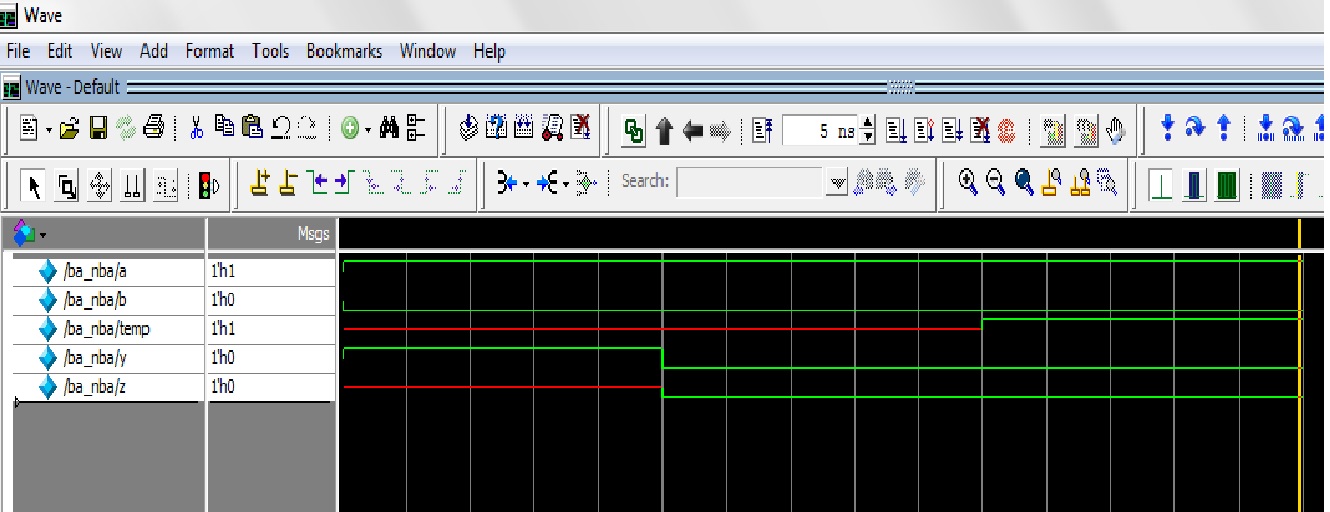

The following example illustrates the Non-Blocking Assignment

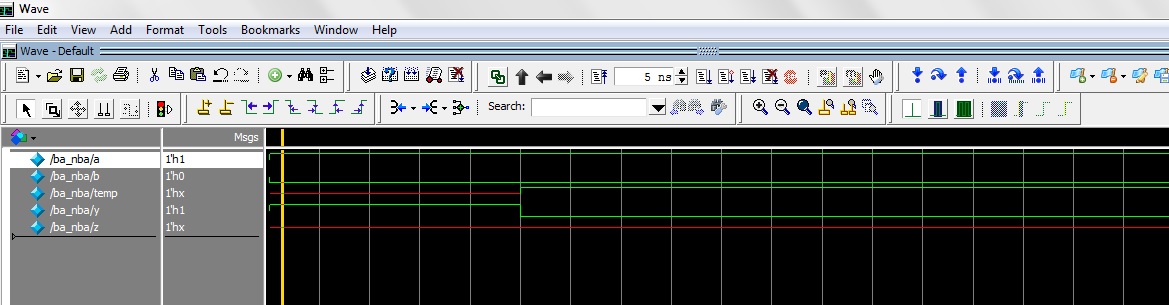

The following example illustrates the Non-Blocking Assignment

initial

begin

a=1;// Use of blocking assignments to initialize

// Blocking and non-blocking assignments can not be used together in a single

// procedural block from the synthesis point of view.

// It is used here for initializing purpose.

b=0;

y<=1; // At 0 simulation time y gets 1.

y<=#5 a&b; // at 5 time units y gets updated

z<=y; // z has only 'X' as value it does not get updated as reg initializes

// to X and it does take the previous value of y which is X not 1 as y has a NBA on it.

#5 temp<=a; // temp gets the value at 5 time units executes at 5 only as above delay is propagation delay

// with NBA.

end

Wave forms for the above example

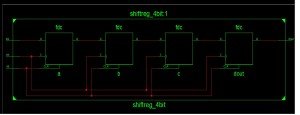

Example (a) Synthesis view of four bit shift reg.

module shiftreg_4bit(dout,clk,rst,din); input clk,rst,din; output reg dout; reg a,b,c; always @ (posedge clk or posedge rst) begin if (rst) begin dout<=0; a<=0; b<=0; c<=0; end else begin a<=din; // Non-Blocking assignments here will hold the previous value and assign on the clock edge, b<=a; // implementing four registers as in conventional shift register. c<=b; dout<=c; end end endmodule

but if changed into Blocking Assignments.

begin a=din; b=a; c=b; // Now blocking assignments will immediately update their values and will collapse into a wire dout=c; //resulting in a single flip flop. end

Example (b) Example for scheduling.

module clk_ba_nba(); reg clk; initial clk<=1; always @ (clk) #5 clk<=~clk; // NBA on clk update after the event, accounted as a change for always block, clock toggles endmodule

but if changed assignments to Blocking Assignments

module clk_ba_nba(); reg clk; initial clk=1; always @ (clk) #5 clk=~clk; // Clk gets updated in the active region, change not accounted, clock does not toggle. endmodule

P.S Whenever you want to implement a fast event independent circuit like combinational circuits where the present value gets updated immediately, Use blocking assignments and whenever there are assignments that to be made together after an event use NBA, usually in sequential circuits.