Qualcomm Interview Question Bank continued from Part 1…

Q : Draw the circuit diagram for a random number generator.

A : Following are the circuits for a random number generator (RNG),

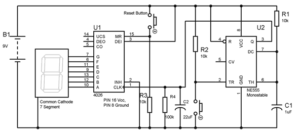

(i) using IC 555 timer, IC 4026 and 7-segment,

RNG circuit using IC 555 timer, IC 4026 and 7-segment (Source : www.circuitstoday.com)

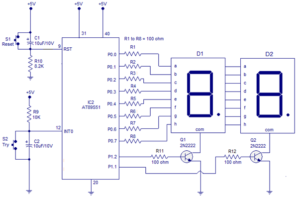

(ii) using 8051 and 7-segment,

RNG circuit using 8051 and 7-segment (Source : www.circuitdigest.com)

Q : What are the advantages and disadvantage of IIR and FIR filters?

A : The following table lists the main differences between FIR and IIR filters,

|

FIR |

IIR |

| Always stable |

Can be unstable |

|

No analog history |

Derived from analog |

|

Linear phase |

No particular phase |

|

Higher order |

Lower order |

|

Requires more memory |

Requires lesser memory |

|

Have numerator only |

Have both numerator and denominator |

|

Used as anti-aliasing, low-pass and band-pass filters |

Used as notch (band-stop) filter |

|

Less efficient |

More efficient |

|

Consume lower power |

Consume more power |

Q : Explain linear phase in FIR filters.

A : FIR filters have a linear phase property which states that the phase is a linear function of frequency and ensures that signals of all the frequencies are delayed by an equal amount of time and thus eliminates the possibility of phase distortion. This property finds applications in audio applications.

Q : What is the architecture of Blackfin processors?

A : The Blackfin is a family of 16 or 32-bit microprocessors manufactured and marketed by Analog Devices. The architecture of Blackfin consists of Data Arithmetic Unit (DAU), Address Arithmetic Unit (AAU), and Sequencer Unit (SU).

DAU consists of two 16-bit MACs, two 40-bit ALUs, four 8-bit Video ALUs and Single Barrel Shifter.

AAU consists of two Data Address Generators (DAGs) that provide addresses for simultaneous dual operand fetches from memory and share a register file that contains four sets of 32-bit index (I), length(L), base(B), and modify(M) registers. There are also eight additional 32-bit address registers that can be used as pointers for general indexing of variables and stack locations.

Program SU is responsible for controlling the flow of execution of instruction and performing conditional jumps, subroutine calls and nested zero-overhead looping. A multi-stage fully interlocked pipeline ensures execution of expected code and that all data hazards are hidden from the programmer.

(Continued to Part 3…)

Gautam Vashisht