There are Two types of Procedural Assignments in Verilog.

- Blocking Assignments

- Nonblocking Assignments

To learn more about Delay: Read Delay in Assignment (#) in Verilog

Blocking assignments

- Blocking assignments (=) are done sequentially in the order the statements are written.

- A second assignment is not started until the preceding one is complete. i.e, it blocks all the further execution before it itself gets executed.

Example:

module Blocking(

input a, // Assume a=1 initialized at time '0'

input b, // Assume b=0 initialized at time '0'

output reg c,

output reg d

);

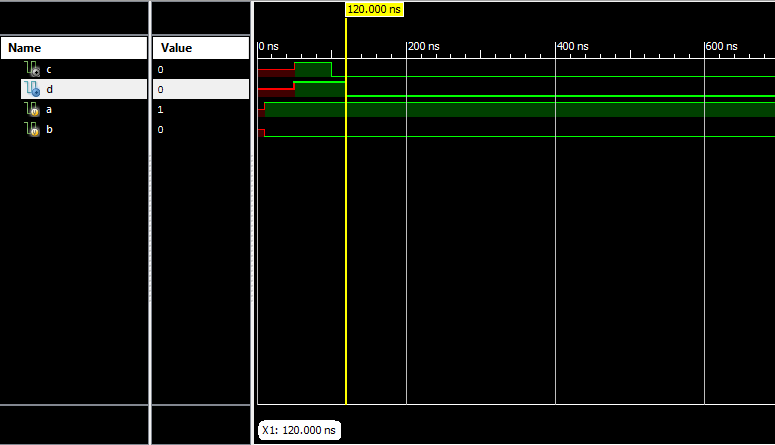

initial

begin

#50 c = a|b; // waits for 50 time units, and execute c = a|b=1

d = c; // Time continues from last line, d=1=c at t=50

c = #50 a&b; // Time continues from last line, a&b = 0 at t = 50, c = 0 = a&b at t=100

#20 d = c; // Time continues from last line, waits for 20 time units. c = 0 at t = 120, d = 0 = c at t = 120

end

endmodule

Non-Blocking assignments

- Nonblocking assignments (<=), which follow each other in the code, are started in parallel.

- The right hand side of nonblocking assignments is evaluated starting from the completion of the last blocking assignment or if none, the start of the procedure.

- The transfer to the left hand side is made according to the delays. An intra- assignment delay in a non-blocking statement will not delay the start of any subsequent statement blocking or non-blocking. However normal delays are cumulative and will delay the output.

- Non-blocking schedules the value to be assigned to the variables but the assignment does not take place immediately. First the rest of the block is executed and the assignment is last operation that happens for that instant of time.

Example:

module Non_Blocking(

input a, // Assume a=1 initialized at time '0'

input b, // Assume b=0 initialized at time '0'

output reg c,

output reg d

);

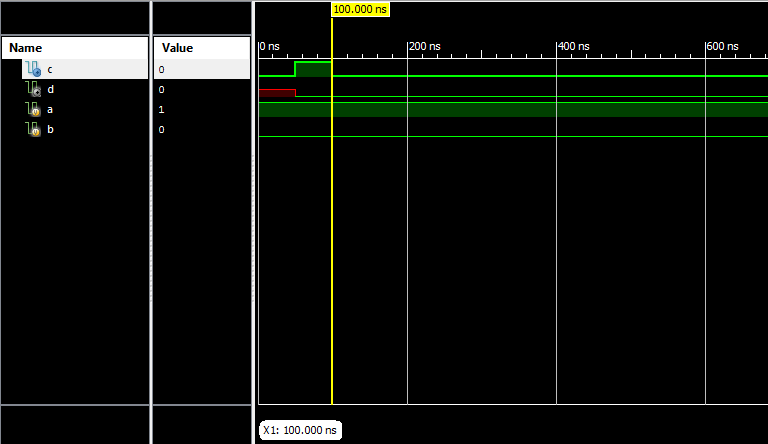

initial

begin

c <= 0;

#50 c <= a|b; // a|b executes at t=0 then wait for 50 units, and execute c=1

d <= c; // The RHS value ‘c’ is ‘0’ at time t=0. Assignment time continues from last line, d=0 at t=50

c <= #50 a&b; // a&b=0 execute at t=0. For assignment time continues from last line, c=0 = a&b at t=100

end

endmodule

To learn more about Blocking and Non_Blocking Assignments: Read Synthesis and Functioning of Blocking and Non-Blocking Assignments

The following example shows interactions between blocking and non-blocking for simulation only (not for synthesis).

Example:

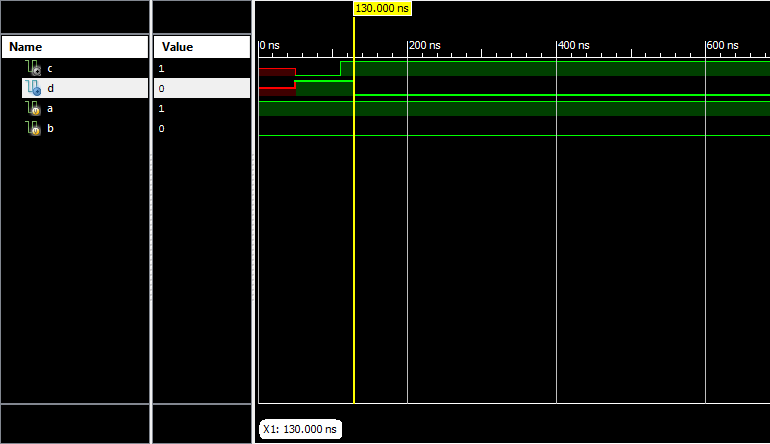

module Mix_Blocking_Non_Blocking(

input a, // Assume a=1 initialized at time '0'

input b, // Assume b=0 initialized at time '0'

output reg c,

output reg d,

);

initial

begin

#50 c = a&b; // wait for 50 units, then grab a,b and execute c = a&b = 0

d = a; // Time continues from last line, d= 0 = a at t=50

c <= #60 a|b; // grab a|b at at t=50, make c=1 = a|b at t= 50+60 = 110

d <= #80 b|c; //grab b|c at at t=50 [b = 0 & c = 0], make d=0 = b|c at t= 50+80 = 130

end

endmodule

For Synthesis (Points to Remember):

- One must not mix “<=” or “=” in the same procedure.

- “<=” best mimics what physical flip-flops do; use it for “always @ (posedge clk..) type procedures.

- “=” best corresponds to what c/c++ code would do; use it for combinational procedures.